| DDR工作原理 | 您所在的位置:网站首页 › viol in是什么意思 › DDR工作原理 |

DDR工作原理

|

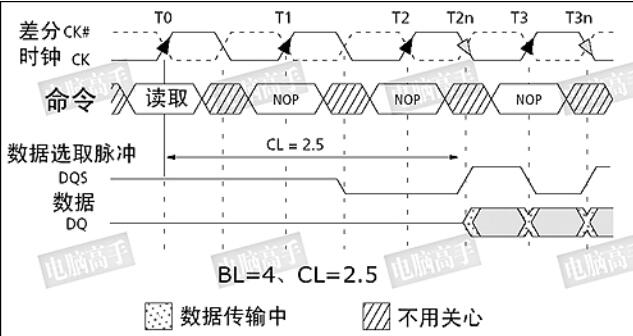

DDR=Double Data Rate双倍速率同步动态随机存储器。严格的说DDR应该叫DDR SDRAM,人们习惯称为DDR,其中,SDRAM 是Synchronous Dynamic Random Access Memory的缩写,即同步动态随机存取存储器。本文首先介绍了DDR工作原理及结构图,其次阐述了DDR DQS信号的处理,具体的跟随小编一起来了解一下。 DDR工作原理及结构图DDR的基本原理 有很多文章都在探讨DDR的原理,但似乎也不得要领,甚至还带出一些错误的观点。首先我们看看一张DDR正规的时序图。

从中可以发现它多了两个信号: CLK#与DQS,CLK#与正常CLK时钟相位相反,形成差分时钟信号。而数据的传输在CLK与CLK#的交叉点进行,可见在CLK的上升与下降沿(此时正好是CLK#的上升沿)都有数据被触发,从而实现DDR。在此,我们可以说通过差分信号达到了DDR的目的,甚至讲CLK#帮助了第二个数据的触发,但这只是对表面现象的简单描述,从严格的定义上讲并不能这么说。之所以能实现DDR,还要从其内部的改进说起。

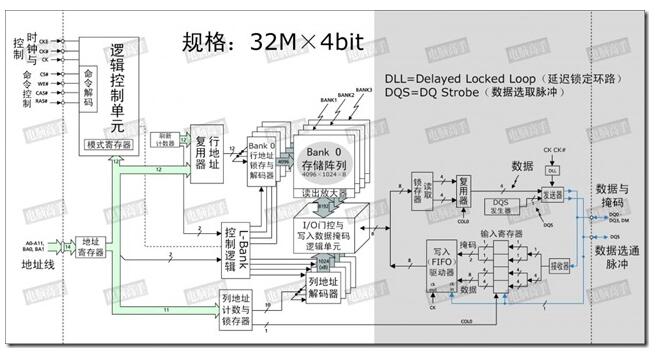

DDR内存芯片的内部结构图 这是一颗128Mbit的内存芯片,从图中可以看出来,白色区域内与SDRAM的结构基本相同,但请注意灰色区域,这是与SDRAM的不同之处。首先就是内部的L-Bank规格。SDRAM中L-Bank 存储单元的容量与芯片位宽相同,但在DDR SDRAM中并不是这样,存储单元的容量是芯片位宽的一倍,所以在此不能再套用讲解SDRAM时 “芯片位宽=存储单元容量” 的公式了。也因此,真正的行、列地址数量也与同规格SDRAM不一样了。 以本芯片为例,在读取时,L-Bank在内部时钟信号的触发下一次传送8bit的数据给读取锁存器,再分成两路4bit数据传给复用器,由后者将它们合并为一路4bit数据流,然后由发送器在DQS的控制下在外部时钟上升与下降沿分两次传输4bit的数据给北桥。这样,如果时钟频率为100MHz,那么在I/O端口处,由于是上下沿触发,那么就是传输频率就是200MHz。 现在大家基本明白DDR SDRAM的工作原理了吧,这种内部存储单元容量(也可以称为芯片内部总线位宽)=2×芯片位宽(也可称为芯片I/O总线位宽)的设计,就是所谓的两位预取(2-bit Prefetch),有的公司则贴切的称之为2-n Prefetch(n代表芯片位宽)。 DDR DQS信号的处理一、DDR 1&2&3总线概览 DDR全名为Double Data Rate SDRAM ,简称为DDR。现在DDR技术已经发展到了DDR 3,理论上速度可以支持到1600MT/s。DDR总线走线数量多,速度快,操作复杂,探测困难,给测试和分析带来了巨大的挑战。 DDR本质上不需要提高时钟频率就能加倍提高SDRAM的速度,它允许在时钟的上升沿和下降沿读出数据,因而其速度是标准SDRAM的两倍。至于地址与控制信号则与传统SDRAM相同,仍在时钟上升沿进行数据判断。 目前,许多计算机使用时钟频率为533MHz的DDR2内存,更先进的DDR2内存正在日益普及,它的时钟频率在400 MHz-800 MHz之间,新的DDR3内存的时钟频率则可以工作在800MHz-16OOMHz之间。DDR3内存芯片还有另外一个长处:更低的能耗,它的运行电压是1.5伏,低于DDR2内存芯片的1.8伏和DDR1内存芯片的2.5伏。在使用电池的设备中能够延长电池续航时间,因为能耗低,产生的热量也就少,从而对冷却的要求也就低一些。 DDR 2&3几个新增特性的含义是:ODT( On Die Termination),DDR1 匹配放在主板上,DDR2&3把匹配直接设计到DRAM芯片内部,用来改善信号品质。OCD(Off Chip Driver)是加强上下拉驱动的控制功能,通过减小DQS与/DQS(DQS是数据Strobe,源同步时钟,数据的1和0由DQS作为时钟来判断) Skew(时滞)来增加信号的时序容限(Timing Margin)。Posted CAS是提高总线利用率的一种方法。AL(Additive Latency)技术是相对于外部CAS,内部CAS执行一定的延时。

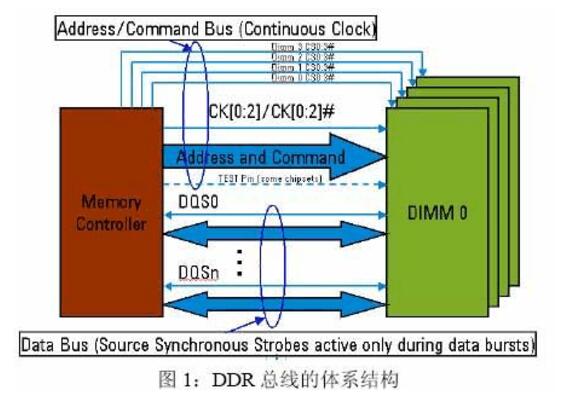

图1是DDR总线的体系结构。其中DQS是源同步时钟,在接收端使用DQS来读出相应的数据DQ,上升沿和下降沿都有效。DDR1总线,DQS是单端信号,而DDR2&3, DQS则是差分信号。DQS和DQ都是三态信号,在PCB走线上双向传输,读操作时,DQS信号的边沿在时序上与DQ的信号边沿处对齐,而写操作时,DQS信号的边沿在时序上与DQ信号的中心处对齐,参考图2,这就给测试验证带来了巨大的挑战:把“读”信号与“写”信号分开是非常困难的!

图2中,Addr/Cmd Bus意思是地址/命令总线,都是时钟的上升沿有效,其中命令由:/CS(片选),/RAS, /CAS,/WE(写使能)决定,比如:“读”命令为:LHLH,“写”命令为:LHLL等。操作命令很多,主要是NOP(空超作),Active(激活),Write,Read,Precharge (Bank关闭),Auto Refresh或Self Refresh(自动刷新或自刷新)等(细节请参考:Jedec规范JESD79)。Data Bus是数据总线,由DQS的上升沿和下降沿判断数据DQ的0与1。 二、DDR 1&2&3总线的信号完整性测试 DDR总线PCB走线多,速度快,操作时序复杂,很容易出现失效问题,为此我们经常用示波器进行DDR总线的信号完整性测试和分析,通常的测试内容包括: 1,命令信号的波形和时序参数:需要测试/RAS,/CAS,/WE,/CS的信号品质,如Vmax(最大电压值),Vmin(最小电压值),Slew Rate(斜率),Ringback(回沟)等;还需要测试相对于时钟边沿的Setup Time(建立时间)和Hold Time(保持时间)。测试相对于时钟边沿的建立时间和保持时间时,需要注意参考电平的位置和最差情况波形的捕获。如图3的/CS建立时间和保持时间的测试就没有测试出最差的建立时间和保持时间值,为此,我们需要用眼图累积的方式设法找到最差情况下的建立时间和保持时间。

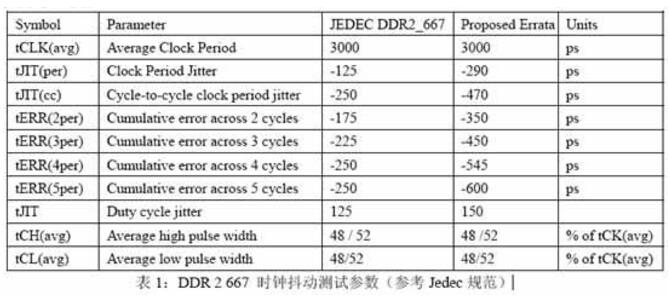

2,地址信号的波形和时序参数:测试内容和测试方质和相对于时钟边沿的建立时间和保持时间的测试。 3,时钟信号的波形和抖动参数:测试建议用差分探头。波形参数包括overshoot(过冲),undershoot(下冲),Slew Rate(斜率)或Rise Time(上升时间)和Fall Time(下降时间),高低时间和Duty Cycle(占空比失真)等。时钟抖动一般只是测试Cycle-Cycle Jitter(周期到周期抖动),但是当速率超过533MT/s的DDR2&3时,则测试内容相当多,不可忽略,下表1是DDR2 667的规范参数。这些抖动参数的测试需要用专用软件实现。

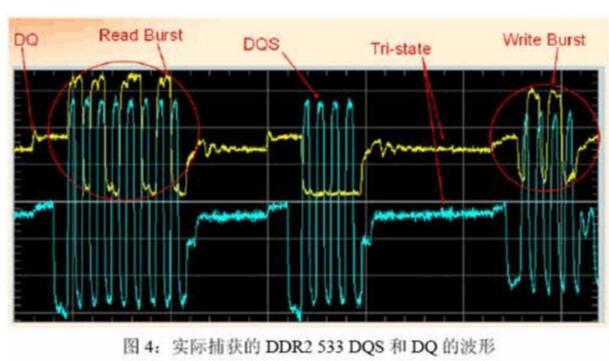

4,速据信号的波形和时序参数:DQS(源同步时钟)和DQ(数据)波形参数与命令地址测试类似,测试起来比较简单,但是探测却比较复杂和困难。DDR1,DQS是单端信号,可以用单端探头测试,DDR2&3 DQS则是差分信号,建议用差分探头测试,减小探测难度。DQS和DQ的时序关系,即相对的在不同操作条件下的建立时间和保持时间关系则非常复杂,分析比较困难,图4是实际捕获的DDR2 533 DQS和DQ的波形。从图中可以看出DQS和DQ的三态(Tri-state)特征,读数据(Read Burst)和写数据(Write Burst)的DQS和DQ的相对时序特征。在我们测试时,只是捕获了这样的波形,然后测试出在“读”“写”操作时的建立时间和保持时间参数是不够的,因为数据码型是变化的,猝发长度也是变化的,只测了几个时序参数很难覆盖各种情况,更难测出最差情况。很多工程师花了一周去测试DDR,仍然测不出问题的关键点就在此处。因此我们应该用眼图的方式去测试DDR的读写时序,确保反映整体时序情况和捕获最差情况下的波形,最好能够套用串行数据的分析方法,调用模板帮助判断。

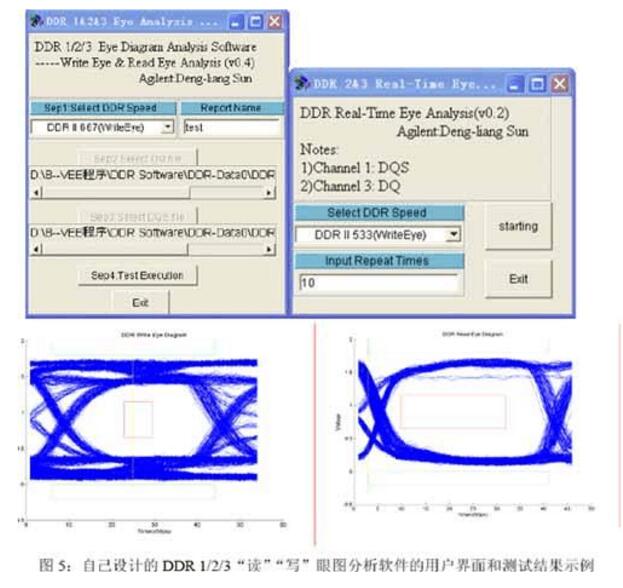

三、DR 1&2&3 “读”“写”眼图测试 基于DDR“读”“写”信号相位不同的特征,本人设计了一个软件进行“读”“写”眼图的测试分析,软件使用VEE Pro 7.5设计界面,使用VEE Pro内嵌的Matlab脚本分析数据,基于规范的AC参数设计模板,帮助工程师进行DDR信号完整性测试分析的最复杂部分即“读” “写”数据眼图的测试分析。 图5是软件界面和分析结果的一个示例,上面两福图形是用户界面。左边的是离线分析软件,用示波器同时采集DQS和DQ信号,并且存为*.CSV文件。采集时,采样率设置为20GSa/s,存储深度设置为200k以上,确保捕获足够的数据,同时被测系统运行大型的软件或MemoryTest.exe工具(此内存测试软件能够进行内存总线的加压测试,一般做系统设计的或内存设计的都有),以让总线上有足够多的数据,来增加捕获各种码型和最差情况的可能性。离线软件调用采集的波形,自动去掉三态数据,把“读”数据放在一起,把“写”数据放在一起,基于DQS的有效边沿(去掉预调整和后调整后的上升边沿和下降边沿),累积在一起形成眼图,调用模板判断信号的优劣和是否满足规范要求。 图5右上图是基于Agilent的DSO80000和54850系列示波器的在线实时分析软件界面。需要把软件安装在示波器内部,或安装在外部电脑上用LAN或GPIB到USB适配器(82357A)连接到示波器。示波器的通道1探测DQS,通道3探测DQ,被测系统上运行大型的软件或MemoryTest.exe工具。在在线软件上输入想重复捕获波形的次数,然后按“starting”进行实时数据的捕获和实时眼图的分析,软件会控制示波器捕获波形,然后分析数据,形成眼图,调用模板判断信号是否满足规范要求,然后重复下一次捕获和分析,同时把新捕获的波形累积到前面捕获的波形上面。在线软件执行的算法与离线软件类似,只是可以自动控制示波器,进行波形的多次捕获和分析,并同时把实时捕获的波形的分析结果连同以前的结果一同显示出来。

图5下面的两个波形是实际的分析结果示例,分析的是DDR2 667,测试点是在DIMM内存条上。对我们比较有意义的是左边的“写”眼图,它反映的是信号从北桥发出,通过主板较长距离传输到达DRAM接收芯片的波形,这是我们做系统设计和测试时需要得到的眼图。右图则是直接从DRAM芯片发出的信号的波形,因为测试点是在DIMM上,所以对我们只有参考价值:当在北桥测试出时序问题时,通过此波形的观察确定是主板设计的问题,还是DIMM或DRAM芯片本身的问题。如果测试点在北桥,则我们需要关注“读”眼图,而此时“写”眼图一般只有参考价值。

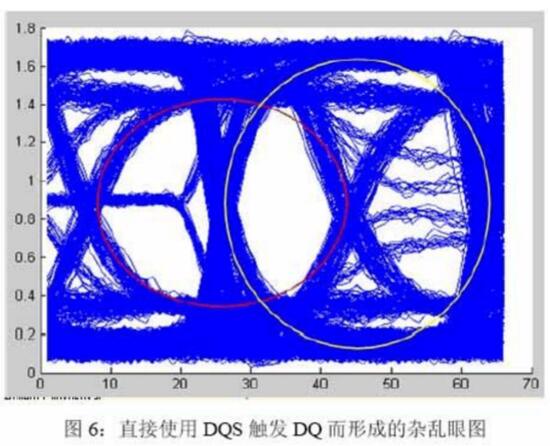

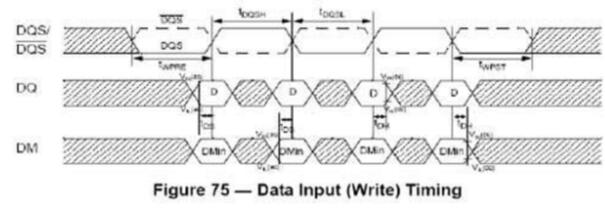

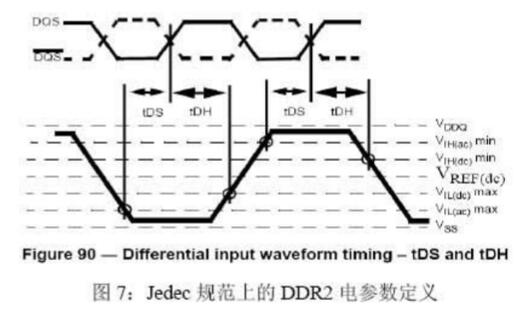

这个DDR“读”“写”眼图分析软件的算法是什么呢?其实很简单,如图6所示,如果直接用DQS触发DQ,则会形成比较乱的眼图,但是中间又包括需要的信息,如图中的红色圆圈周围的是“写”眼图信息,途中的黄色圆圈周围则是“读”眼图信息。而眼图之所以乱,是因为同时包括“三态”信号和“读”“写”信号,而“读” 和“写”信号的时序是矛盾的。使用 软件进行分离的处理比较容易:首先,扔掉三态信号,保留有用信息,软件设计时,检测DQS有效边沿,离DQS有效边沿较远的信号就是三态信号,扔掉它;然后,根据建立时间和保持时间的关系把“读”信号和“写”信号分成两个数据库;最后,把“读”信号数据库按DQS有效边沿放在一起形成眼图,把“写”信号数据库按DQS有效边沿放在一起形成眼图,分别调用模板产生测试结果。 四、DDR 1&2&3 模板定义 DDR规范没有定义模板,这给用眼图方式分析信号时判断信号是否满足规范要求带来挑战。为了更容易判断是否满足规范的要求,像分析一般串行信号一样分析“读”“写”眼图,本人根据Jedec规范设计了“读”“写”模板。下面以定义“写”眼图模板为例,介绍一下模板的设计方法。 图7是Jedec规范上的时序和波形参数,tDS是相对于DQS有效边沿的建立时间,tDH是相对于DQS有效边沿的保持时间,tDS相对于DQ的AC参数,tDH则相对于DQ的DC参数,不过为了测试方面的方便性,我们都可以用AC参数来定义tDS和tDH。tDS和tDH参数的测试是DDR的核心测试参数。

在Jedec规范上,我们可以查到各种速率的tDS和tDH 的规范值,比如DDR2 533,tDS 是100ps,tDH 是225ps。我们也可以查到各种速率的AC参数值,比如DDR2 533:其中,VIH(ac)min是VIH(ac)规范的最小值,VIL(ac)max是VIL(ac)规范的最大值,Vref是参考电压,对DDR1来说是1.25V,DDR2来说是0.9V,DDR3来说是0.75V。

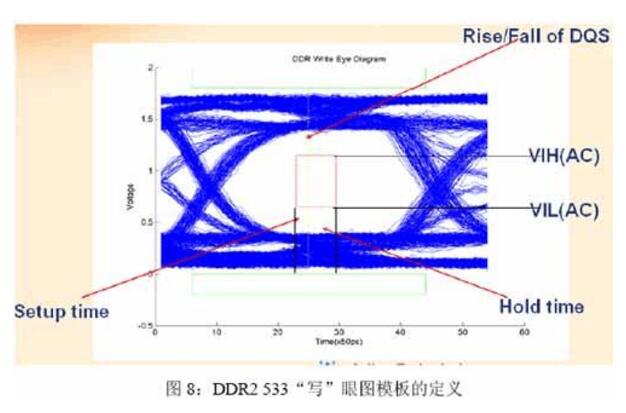

基于tDS和tDH 和VIH(ac)min和VIL(ac)max参数,我们可以得出DDR2 533“写”眼图的模板如图8示。中间的红色区域就是模板,Setup time是tDS建立时间,Hold time是tDH 保持时间,VIH(AC)是VIH(ac)min值,VIL(AC)是VIL(ac)max值。中间的黄色线是DQS的有效边沿即有效的上升沿或下降沿。

严格按规范的话,中间的模板应该定义为横着的梯形,因为保持时间是相对于DC参数,不过用长方形可以定义一个更严格的参数要求。 五、小结 DDR是需要进行信号完整性测试的总线中最复杂的总线,不仅走线多、探测困难,而且时 序复杂,各种操作交织在一起。本文基于多年的实践经验,提供了一些测试的参考方法,尤其对 “读”“写”眼图的测试方法和模板的定义提出一种创新的观点,并设计软件实现了这种方法,希望对主板,DIMM,DRAM设计者和测试者有参考价值。 |

【本文地址】